# Dual-Gated Topological Insulator Thin-Film Device for Efficient Fermi-Level Tuning

Fan Yang, A. A. Taskin, Satoshi Sasaki, Kouji Segawa, Yasuhide Ohno, Kazuhiko Matsumoto, and Yoichi Ando<sup>\*</sup>

Institute of Scientific and Industrial Research, Osaka University, Ibaraki, Osaka 567-0047, Japan

**ABSTRACT** Observations of novel quantum phenomena expected for threedimensional topological insulators (TIs) often require fabrications of thin-film devices and tuning of the Fermi level across the Dirac point. Since thin films have both top and bottom surfaces, an effective control of the surface chemical potential requires dual gating. However, a reliable dual-gating technique for TI thin films has not yet been developed. Here we report a comprehensive method to fabricate a dual-gated TI device and demonstrate tuning of the chemical potential of both surfaces across the Dirac points. The most important part of our method is

the recipe for safely detaching high-quality, bulk-insulating  $(Bi_{1-x}Sb_x)_2Te_3$  thin films from sapphire substrates and transferring them to Si/SiO<sub>2</sub> wafers that allow back gating. Fabrication of an efficient top gate by low-temperature deposition of a SiN<sub>x</sub> dielectric complements the procedure. Our dual-gated devices are shown to be effective in tuning the chemical potential in a wide range encompassing the Dirac points on both surfaces.

**KEYWORDS:** topological insulator  $\cdot$  (Bi<sub>1-x</sub>Sb<sub>x</sub>)<sub>2</sub>Te<sub>3</sub>  $\cdot$  electrostatic gating  $\cdot$  MBE  $\cdot$  Dirac fermion

hree-dimensional (3D) topological insulators (TIs) harbor spin-momentumlocked surface states forming a Dirac cone.<sup>1-3</sup> The resulting spin-nondegenerate Dirac fermions inhabiting the surface of 3D TIs hold promise for various novel phenomena such as topological magnetoelectric effects,<sup>4,5</sup> proximity-induced topological superconductivity associated with Majorana fermions,<sup>6</sup> and topological exciton condensation,<sup>7</sup> all of which would provide fundamentally new device principles. Realizations of those novel phenomena require fine control of the surface chemical potential, which is best achieved by electrostatic gating.

So far, both back gating<sup>8,9</sup> and top gating<sup>10–13</sup> have been successfully applied to 3D TI thin films, but with a single gate the chemical potential of only one surface (bottom or top) can be effectively tuned, and the other surface is not controlled simultaneously unless the samples are ultrathin.<sup>14</sup> Unfortunately, this is not sufficient for many applications: For example, the topological magnetoelectric effects require the chemical potential of the whole

surface of a 3D TI to be tuned to the Dirac point, which is to be gapped by time-reversal-breaking perturbations; also, the topological exciton condensation requires the top and bottom surfaces to contain equal numbers of Dirac electrons and holes, respectively (or *vice versa*). Furthermore, in a new type of topological insulator called a topological crystalline insulator,<sup>3</sup> dual gating will controllably break mirror symmetry and allow a fundamentally new type of transistor device.<sup>15</sup> Obviously, efficient dual-gating techniques should be developed for future studies of 3D TIs.

In this paper, we report our successful development of a comprehensive method to fabricate a highly tunable dual-gated TI device based on bulk-insulating  $(Bi_{1-x}Sb_x)_2Te_3$  thin films. Our device is made of large-area thin films rather than exfoliated single crystals, and all fabrication processes are done only with photolithography, both of which are important ingredients for future industrial applications. In the case of nanodevices based on exfoliated platelets, back gating is relatively easy, because one can directly exfoliate the TI materials onto Si/SiO<sub>2</sub> substrates that allow

\* Address correspondence to y\_ando@sanken.osaka-u.ac.jp.

Received for review January 7, 2015 and accepted April 8, 2015.

Published online April 08, 2015 10.1021/acsnano.5b00102

© 2015 American Chemical Society

VOL. 9 • NO. 4 • 4050-4055 • 2015

4050

back gating. The back gating is more difficult for thinfilm devices, because epitaxial growth of TI thin films on a thin dielectric is not a straightforward task. In the past, a SrTiO<sub>3</sub> substrate has been used for back gating, utilizing its ultrahigh dielectric constant at low temperatures, but this limits both the choice of better substrates for film growth and the working temperature of the back gate. In terms of the film guality, a sapphire substrate is among the best for  $Bi_2Se_3^{16,17}$  and  $Bi_2Te_{31}^{18}$  but gating through a sapphire substrate is impractical. Recently, it was reported<sup>19</sup> that high-guality Bi<sub>2</sub>Se<sub>3</sub> films grown on a sapphire substrate can be transferred to other substrates by using buffered oxide etch (BOE) or a potassium hydroxide (KOH) solution to peel off the films from the sapphire substrates. The present work builds on this progress. Our device is based on thin films of bulk-insulating  $(Bi_{1-x}Sb_x)_2Te_3^{20}$ grown on sapphire substrates by molecular beam epitaxy (MBE), which are subsequently peeled off and transferred to a Si/SiO<sub>2</sub> substrates. Since we found that neither BOE nor KOH works well for  $(Bi_{1-x}Sb_x)_2Te_3$ , we have developed an improved, damage-free method for the film transfer.

Fabrications of top gates on TIs are notorious for damaging the top surface mobility and introducing localized states to pin the chemical potential, which works against effective gate tuning;<sup>21</sup> nevertheless, several groups have recently made progress in this respect. For example, our group employed hot-wire chemical vapor deposition (CVD) of a SiN<sub>x</sub> dielectric layer at low temperature and successfully fabricated an efficient top gate without degrading the mobility.<sup>11</sup> Other groups employed atomic-layer deposition (ALD) of an  $Al_2O_3$  dielectric layer at low temperature<sup>12</sup> or used exfoliated h-BN platelets<sup>22</sup> for preserving the quality of the surface beneath the top gate. In the present work, we used the SiN<sub>x</sub> dielectric layer deposited by hot-wire CVD to fabricate a top gate. The dualgate structure of our device turns out to be effective in tuning the chemical potential of the top and bottom surfaces across the Dirac point.

## **RESULTS AND DISCUSSION**

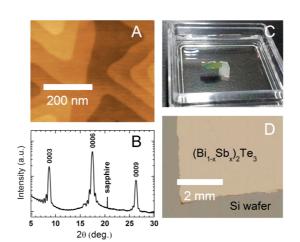

The epitaxial  $(Bi_{1-x}Sb_x)_2Te_3$  (hereafter called BST) thin films were grown on sapphire (0001) substrates by using an MBE technique (see the Methods for details).<sup>23</sup> In this paper, we focus on 17 nm thick films with x = 0.15, which is optimized for the bulk-insulating property. The thickness was measured with an atomicforce microscope (AFM), which is also used for confirming the epitaxial growth with large, atomically flat terraces (Figure 1A). The X-ray diffraction data for small angles show clear Kiessig fringes (Figure 1B), which testifies to the homogeneity of the thickness.

After the MBE growth, we transferred the BST films from sapphire to Si/SiO<sub>2</sub> substrates. According to the previously reported method, which works for Bi<sub>2</sub>Se<sub>3</sub>

Figure 1. (A) AFM image of a 17 nm thick  $(Bi_{1-x}Sb_x)_2Te_3$  film. (B) Low-angle X-ray diffraction patterns of a 28 nm thick  $(Bi_{1-x}Sb_x)_2Te_3$  film. (C) After the peeling-off, the detached  $(Bi_{1-x}Sb_x)_2Te_3/PMMA$  bilayer floats on pure water, while the sapphire substrate sinks down. (D) Optical image of a  $(Bi_{1-x}Sb_x)_2Te_3$  film transferred onto a silicon wafer.

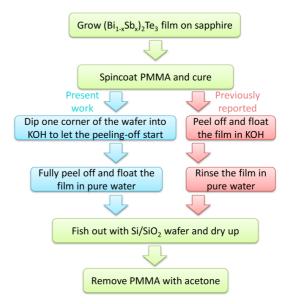

## Figure 2. Diagram of the film-transfer process.

films,<sup>19</sup> in order to peel off the film from the sapphire substrate, the film needs to be floated on BOE or KOH solution. However, in the case of the BST films, we found that both BOE and KOH cause problems. The BST films cannot be detached in BOE; in KOH, the peeling-off occurs smoothly, but the BST film is chemically attacked and degraded (see the Supporting Information). Therefore, we developed a new transfer method using distilled water to avoid the degradation of the BST film due to KOH. As demonstrated in the Supporting Information, the morphology of the films does not present any noticeable degradation after the transfer (Figure S2); also, the carrier concentration and the mobility of the BST films transferred by this method are comparable to those of the as-grown films (Figure S3).

The transfer of the films was done in the steps described in detail in the Methods section (see Figure 2

IAI

for a diagram). Essentially, the film is spin-coated with the polymethyl methacrylate (PMMA), and the peeling-off process of the BST/PMMA bilayer is initiated by dipping only one corner of the substrate into a KOH aqueous solution, followed by complete detachment in distilled water (Figure 1C). The BST/ PMMA bilayer floating on the water is taken out with

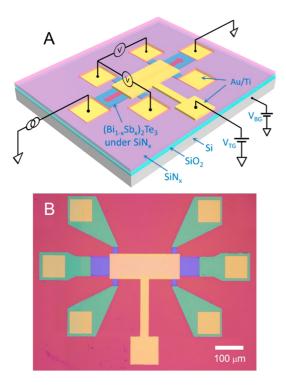

Figure 3. (A) Schematics of the device structure and measurement configuration. (B) Optical image of a typical device.

a Si or Si/SiO<sub>2</sub> wafer, and the PMMA layer is removed with acetone to complete the transfer process (Figure 1D). After the transfer of the film to the Si/SiO<sub>2</sub> wafer, we fabricated the top gate using the process described in ref 11 (see Methods section for details). The optical photograph and the schematic of our device are shown in Figure 3.

The measurements of the sheet resistance ( $R_{sh}$ ) and the Hall resistance ( $R_{yx}$ ) were made on the Hall bar at T = 1.8-300 K. The top- and back-gate voltages ( $V_{TG}$ and  $V_{BG}$ , respectively) were applied in the range of  $\pm 90$  V. We note that, when the top-gate voltage is cycled, a hysteresis due to trapped charges was observed in both  $R_{sh}$  and  $R_{yx}$ ; hence, to avoid confusion, all the presented curves were taken with a decreasing gate voltage from +90 to -90 V.

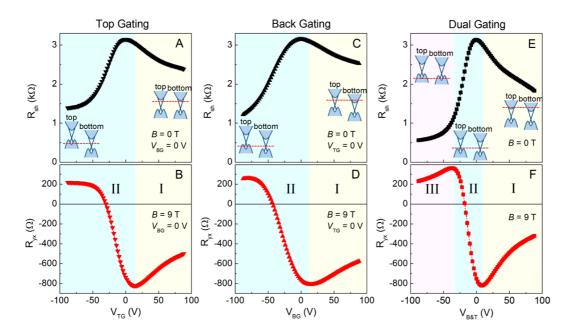

Figure 4 shows a comparison of the gating effects seen in  $R_{sh}$  and  $R_{yx}$  (in B = 9 T) at T = 1.8 K for three gating configurations: top, back, and dual gating. In the case of dual gating, the same voltage was applied to both top and back gates.

In order to understand the gating result, one should notice the existence of a finite capacitive coupling between the top and bottom surface states for thin bulk-insulating TI devices (see Supporting Information for full modeling).<sup>11,22</sup> Due to the capacitive coupling, the two surfaces are not tuned independently. When a voltage is applied to a single gate, the chemical potential of the other surface is also affected. Our previous results<sup>11</sup> show that the coupling ratio (defined as  $\Delta N_{bot}/\Delta N_{top}$ , when  $\Delta V_{TG}$  is applied) is about 50% around the Dirac point for a 20 nm thick BST film. In the present work, the thickness of the film is 17 nm, suggesting that the coupling can be even stronger.

Figure 4. Gate-voltage dependences of sheet resistance ( $R_{sh}$ ) and Hall resistivity ( $R_{yx}$ ) for three different gating configurations: (A, B) top gating, (C, D) back gating, and (E, F) dual gating.

VOL. 9 • NO. 4 • 4050-4055 • 2015 A

www.acsnano.org

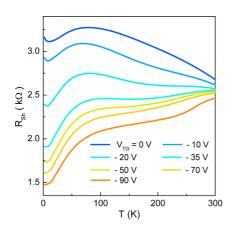

Figure 5. Temperature dependences of the sheet resistance  $(R_{sh})$  at different top-gate voltages.

In the 17 nm thick BST film used for the dual-gated device, at zero gate voltage, it turned out that the carrier type and carrier concentrations of the two surfaces are different, possibly due to the difference in band bending caused by different interfaces: The top surface accommodates a low concentration of p-type carriers, and thus its Fermi level is slightly below the Dirac point; on the other hand, the bottom surface is n-type with a relatively high carrier concentration, corresponding to a Fermi-level position well above the Dirac point.

Due to the high initial concentration of n-type carriers on the bottom surface, for the single top gating (Figure 4A,B) or back gating (Figure 4C,D), only the Fermi level of the top surface can be tuned across the Dirac point, corresponding to the single negative peak in  $R_{vx}(V)$  (Figure 4B,D) and the peak in  $R_{sh}$  at a similar gate voltage (Figure 4A,C). For the convenience of further discussions, we divide the singlegating data (Figure 4A–D) into two regions according to the difference in band diagrams. In region I,  $R_{yx}$  is negative, and  $|R_{yx}|$  increases upon scanning the gate voltage in the negative direction; This means that both surfaces are n-type. On the boundary with region II, the top surface goes across the Dirac point and becomes p-type, and therefore  $|R_{yx}|$  starts to decrease before it reaches zero and changes sign. The sign change indicates that the sample becomes p-type dominated. However, the absence of a positive peak in  $R_{yx}(V)$  suggests that the bottom surface is still n-type.

In contrast, in the case of dual gating (Figure 4E,F), the gate-voltage dependence of  $R_{yx}$  presents *both* negative and positive peaks, and a new region (region III) shows up. In region III,  $R_{yx}$  is positive, and  $|R_{yx}|$  decreases upon scanning the dual-gate voltage  $(V_{B\&T})$  in the negative direction; this means that both surfaces are now tuned to be p-type. Therefore, with the help of additional positive carriers provided by the top gate, the back gate is now able to bring down the chemical potential of the bottom surface to cross the

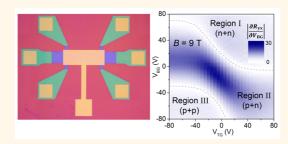

Figure 6. 2D plots of (A)  $|\partial R_{\rm sh}/\partial V_{\rm BG}|$  and (B)  $|\partial R_{\rm yx}/\partial V_{\rm BG}|$  as a function of top-gate and back-gate voltages. These data were taken on a different device on the same wafer based on the same batch of the BST film. The dash-dotted lines are a guide to the eyes to trace the locations of the "white bands", which correspond to the locations of the peaks (*i.e.*, zero slope) in the raw data.

Dirac point. It is useful to note that in our device the change in  $R_{sh}$  upon dual gating is as large as a factor of 6 (Figure 4E), which is among the largest ever reported for TI thin-film devices except for the cases of quantum Hall<sup>13,24</sup> or quantum anomalous Hall<sup>12,25,26</sup> effects. The temperature dependences of  $R_{sh}$  for various  $V_{TG}$  from 0 to -90 V are shown in Figure 5. It demonstrates that the gate works effectively in modifying the resistance of the device even at room temperature, which overcomes the working temperature limit of the back gate based on SrTiO<sub>3</sub>.

We have also done experiments to scan both  $V_{TG}$  and  $V_{BG}$  independently (the measurements were made on a different device). Figure 6 shows false-color mappings of  $|\partial R_{sh}/\partial V_{BG}|$  and  $|\partial R_{yx}/\partial V_{BG}|$  in the  $V_{BG}$  vs  $V_{TG}$ plane. The white color corresponds to a positive or negative peak (*i.e.*, zero slope), and hence the two white bands in the  $|\partial R_{yx}/\partial V_{BG}|$  map (Figure 6B) roughly show where the Dirac point is accessed; in other words, the two white bands in Figure 6B separate the regions I, II, and III indicated in Figure 4. By comparing the locations of the white bands in Figure 6A and B, one can see that the peak in  $R_{sh}$  does not necessarily mean that the chemical potential is at the Dirac point in a dual-gate device.<sup>22</sup> The raw data before taking the ARTICLE

JAI

www.acsnano.org

derivative are available in Figure S3 of the Supporting Information.

## CONCLUSION

We have presented a comprehensive method to realize highly efficient dual gating of TI thin films. It combines the transfer of high-quality epitaxial thin films grown on sapphire onto a Si/SiO<sub>2</sub> wafer and top-gate fabrication by using a low-temperature deposition of SiN<sub>x</sub> with hot-wire CVD. This method is

#### **METHODS**

**MEB Growth of BST Films.** The 17 nm thick BST films were grown on sapphire (0001) substrates by MBE. The co-deposition of Bi and Sb (with a flux ratio of 1:5.5) was done in three steps at different substrate temperatures: 5 min at 230 °C, 5 min at 280 °C, and 21 min at 325 °C. The morphology and thickness of the films were measured with AFM.

Transfer of BST Films. After the growth, the BST film was spincoated with PMMA at 5000 rpm for 1 min and cured at 170 °C for 3 min. Then one corner of the substrate was dipped into a 5% KOH aqueous solution to initiate the detachment. During this initial stage, only a small portion of the film at the corner was exposed to the KOH solution. After several minutes, the BST/ PMMA bilayer started to separate from sapphire at the corner. At that point, the substrate was taken out from the KOH solution and the separated corner was then dipped into distilled water; due to the strong surface tension of water, the detached part of the BST/PMMA bilayer would float on the water surface. Then the whole substrate was slowly inserted into the water; during this process, the BST/PMMA bilayer feels a buoyancy force to make it detach from the substrate due to the surface tension of the water. Eventually, the whole BST/PMMA bilayer was fully detached and floated on the water surface (Figure 1C). After that, the floating BST/PMMA bilayer was taken out with a Si/SiO<sub>2</sub> wafer (SiO<sub>2</sub> thickness of 150 nm), dried at room temperature, and treated with acetone to remove PMMA. Finally, the transferred BST film (Figure 1D) was annealed at 120 °C under vacuum for 2 to 7 h to fully get rid of residual water; we found that this final annealing process promoted the insulating property of the film.

**Device Fabrication.** The BST film was patterned into a Hall-bar shape with photolithography and wet etching. The etchant is 1 HCl/0.8 H<sub>2</sub>O<sub>2</sub>/8 CH<sub>3</sub>COOH/16 H<sub>2</sub>O (volume ratio); the mass concentrations of the first three solutions are 36%, 33%, and 99.7%, respectively. Next, metal contacts (5 nm Ti and 50 nm Au) were fabricated with photolithography, thermal evaporation, and lift-off. Then a 200 nm SiN<sub>x</sub> dielectric layer was deposited with hot-wire CVD at *T* < 80 °C, covering the whole wafer. After that, the SiN<sub>x</sub> layer above the metal contacts was removed by photolithography and reactive-ion etching (CF<sub>4</sub>/Ar flow: 20/5 sccm, pressure: 3 Pa, power: 100 W, duration: 3 min). Finally, a top-gate electrode was fabricated by photolithography and Ti/Au deposition.

**Transport Measurements.** The measurements were performed using a standard ac lock-in technique in a cryostat with a base temperature of 1.8 K in magnetic fields up to 9 T. The excitation current was 1  $\mu$ A. The gate voltages were applied using Keithley 2400 source meters.

Conflict of Interest: The authors declare no competing financial interest.

Supporting Information Available: Comparison of the morphology of BST films before and after treatment with a 5% KOH solution, morphology of the BST film after transfer, comparison of transport properties of BST films before and after transfer, magnetic-field dependences of the Hall resistivity at various  $V_{B&T}$ ,  $V_{BG}$  dependences of  $R_{sh}$  and  $R_{yx}$  at various  $V_{TG}$ , and an effective model of the dual gating. This material is available free of charge *via* the Internet at http://pubs.acs.org.

based on large-area thin films and employs only photolithography, both of which are favorable for future industrial applications. We demonstrate that the dual gating allows tuning of the chemical potentials of the top and bottom surfaces across the Dirac point, which is manifested in the  $V_{B&T}$  dependence of  $R_{yx}$  showing a sharp sign change bound by two peaks, and also in  $R_{sh}$ , changing by 6 times with  $V_{B&T}$ . This dual-gating method opens exciting opportunities to realize various novel phenomena expected for 3D TIs.

Acknowledgment. We thank Y. Maekawa for technical assistance, and Nanotechnology Open Facilities (NOF) and Center of Innovation (COI) programs at Osaka University for nanofabrication facilities. This work was supported by JSPS (KAKENHI 25220708 and 25400328), MEXT (Innovative Area "Topological Quantum Phenomena" KAKENHI), AFOSR (AOARD 124038), Inamori Foundation, and the Murata Science Foundation.

#### **REFERENCES AND NOTES**

- Hasan, M. Z.; Kane, C. L. Colloquium: Topological Insulators. *Rev. Mod. Phys.* 2010, 82, 3045.

- Qi, X.-L.; Zhang, S.-C. Topological Insulators and Superconductors. *Rev. Mod. Phys.* 2011, 83, 1057–1110.

- 3. Ando, Y. Topological Insulator Materials. J. Phys. Soc. Jpn. 2013, 82, 102001.

- Qi, X.-L.; Hughes, T. L.; Zhang, S.-C. Topological Field Theory of Time-Reversal Invariant Insulators. *Phys. Rev. B* 2008, 78, 195424.

- Qi, X.-L.; Li, R.; Zang, J.; Zhang, S.-C. Inducing a Magnetic Monopole with Topological Surface States. *Science* 2009, 323, 1184–1187.

- Fu, L.; Kane, C. L. Superconducting Proximity Effect and Majorana Fermions at the Surface of a Topological Insulator. *Phys. Rev. Lett.* **2008**, *100*, 096407.

- Seradjeh, B.; Moore, J. E.; Franz, M. Exciton Condensation and Charge Fractionalization in a Topological Insulator Film. *Phys. Rev. Lett.* **2009**, *103*, 066402.

- Chen, J.; Qin, H. J.; Yang, F.; Liu, J.; Guan, T.; Qu, F. M.; Zhang, G. H.; Shi, J. R.; Xie, X. C.; Yang, C. L.; *et al.* Gate-Voltage Control of Chemical Potential and Weak Antilocalization in Bi<sub>2</sub>Se<sub>3</sub>. *Phys. Rev. Lett.* **2010**, *105*, 176602.

- He, X.; Guan, T.; Wang, X.; Feng, B.; Cheng, P.; Chen, L.; Li, Y.; Wu, K. Highly Tunable Electron Transport in Epitaxial Topological Insulator (Bi<sub>1-x</sub>Sb<sub>x</sub>)<sub>2</sub>Te<sub>3</sub> Thin Films. *Appl. Phys. Lett.* **2012**, *101*, 123111.

- Steinberg, H.; Laloë, J.-B.; Fatemi, V.; Moodera, J. S.; Jarillo-Herrero, P. Electrically Tunable Surface-to-Bulk Coherent Coupling in Topological Insulator Thin Films. *Phys. Rev. B* **2011**, *84*, 233101.

- Yang, F.; Taskin, A. A.; Sasaki, S.; Segawa, K.; Ohno, Y.; Matsumoto, K.; Ando, Y. Top Gating of Epitaxial (Bi<sub>1-x</sub>Sb<sub>x</sub>)<sub>2</sub>Te<sub>3</sub> Topological Insulator Thin Films. *Appl. Phys. Lett.* **2014**, *104*, 161614.

- Checkelsky, J.; Yoshimi, R.; Tsukazaki, A.; Takahashi, K.; Kozuka, Y.; Falson, J.; Kawasaki, M.; Tokura, Y. Trajectory of the Anomalous Hall Effect towards the Quantized State in a Ferromagnetic Topological Insulator. *Nat. Phys.* **2014**, *10*, 731–736.

- Yoshimi, R.; Tsukazaki, A.; Kozuka, Y.; Falson, J.; Takahashi, K.; Checkelsky, J.; Nagaosa, N.; Kawasaki, M.; Tokura, Y. Quantum Hall Effect on Top and Bottom Surface States of Topological Insulator (Bi<sub>1-x</sub>Sb<sub>x</sub>) <sub>2</sub>Te<sub>3</sub> Films. arXiv preprint arXiv:1409.3326, **2014**.

- Kim, D.; Cho, S.; Butch, N. P.; Syers, P.; Kirshenbaum, K.; Adam, S.; Paglione, J.; Fuhrer, M. S. Surface Conduction of Topological Dirac Electrons in Bulk Insulating Bi<sub>2</sub>Se<sub>3</sub>. *Nat. Phys.* 2012, 8, 460–464.

VOL.9 • NO.4 • 4050-4055 • 2015 🕅

- Liu, J.; Hsieh, T. H.; Wei, P.; Duan, W.; Moodera, J.; Fu, L. Spin-Filtered Edge States with an Electrically Tunable Gap in a Two-Dimensional Topological Crystalline Insulator. *Nat. Mater.* 2014, *13*, 178–183.

- Bansal, N.; Kim, Y. S.; Brahlek, M.; Edrey, E.; Oh, S. Thickness-Independent Transport Channels in Topological Insulator Bi<sub>2</sub>Se<sub>3</sub> Thin Films. *Phys. Rev. Lett.* **2012**, *109*, 116804.

- Taskin, A. A.; Sasaki, S.; Segawa, K.; Ando, Y. Manifestation of Topological Protection in Transport Properties of Epitaxial Bi<sub>2</sub>Se<sub>3</sub> Thin Films. *Phys. Rev. Lett.* **2012**, 109.

- Taskin, A. A.; Yang, F.; Sasaki, S.; Segawa, K.; Ando, Y. Topological Surface Transport in Epitaxial SnTe Thin Films Grown on Bi<sub>2</sub>Te<sub>3</sub>. *Phys. Rev. B* **2014**, *89*, 121302.

- Bansal, N.; Cho, M. R.; Brahlek, M.; Koirala, N.; Horibe, Y.; Chen, J.; Wu, W.; Park, Y. D.; Oh, S. Transferring MBE-Grown Topological Insulator Films to Arbitrary Substrates and Metal-Insulator Transition *via* Dirac Gap. *Nano Lett.* **2014**, *14*, 1343–8.

- Zhang, J.; Chang, C.-Z.; Zhang, Z.; Wen, J.; Feng, X.; Li, K.; Liu, M.; He, K.; Wang, L.; Chen, X.; *et al.* Band Structure Engineering in (Bi<sub>1-x</sub>Sb<sub>x</sub>)<sub>2</sub>Te<sub>3</sub> Ternary Topological Insulators. *Nat. Commun.* **2011**, *2*, 574.

- Liu, H.; Ye, P. D. Atomic-Layer-Deposited Al<sub>2</sub>O<sub>3</sub> on Bi<sub>2</sub>Te<sub>3</sub> for Topological Insulator Field-Effect Transistors. *Appl. Phys. Lett.* **2011**, *99*, 052108.

- Fatemi, V.; Hunt, B.; Steinberg, H.; Eltinge, S. L.; Mahmood, F.; Butch, N. P.; Watanabe, K.; Taniguchi, T.; Gedik, N.; Ashoori, R.; *et al.* Electrostatic Coupling between Two Surfaces of a Topological Insulator Nanodevice. *Phys. Rev. Lett.* **2014**, *113*, 206801.

- 23. Taskin, A.; Sasaki, S.; Segawa, K.; Ando, Y. Achieving Surface Quantum Oscillations in Topological Insulator Thin Films of Bi<sub>2</sub>Se<sub>3</sub>. *Adv. Mater.* **2012**, *24*, 5581–5585.

- Brüne, C.; Thienel, C.; Stuiber, M.; Böttcher, J.; Buhmann, H.; Novik, E. G.; Liu, C.-X.; Hankiewicz, E. M.; Molenkamp, L. W. Dirac-Screening Stabilized Surface-State Transport in a Topological Insulator. arXiv preprint arXiv:1407.6537, 2014.

- Chang, C. Z.; Zhang, J.; Feng, X.; Shen, J.; Zhang, Z.; Guo, M.; Li, K.; Ou, Y.; Wei, P.; Wang, L. L.; *et al.* Experimental Observation of the Quantum Anomalous Hall Effect in a Magnetic Topological Insulator. *Science* **2013**, *340*, 167– 70.

- Kou, X.; Guo, S.-T.; Fan, Y.; Pan, L.; Lang, M.; Jiang, Y.; Shao, Q.; Nie, T.; Murata, K.; Tang, J.; *et al.* Scale-Invariant Quantum Anomalous Hall Effect in Magnetic Topological Insulators beyond the Two-Dimensional Limit. *Phys. Rev. Lett.* **2014**, *113*, 137201.